top of page

TSMC A16 Process Technology Explained: Ushering in the Angstrom Era

A deep dive into TSMC's A16 process technology: GAAFET transistors, backside power delivery, performance benefits, and competitive analysis.

What is TSMC 3DFabric? The Chip Stacking Revolution Integrating CoWoS, InFO, and Backside Power Delivery

A deep dive into TSMC’s 3DFabric advanced packaging platform, exploring CoWoS, InFO, and backside power delivery technologies and how they enable the next era of AI and HPC.

What is 2.5D Packaging? A Complete Guide to This Key Semiconductor Innovation

Discover how 2.5D packaging works and why it’s vital for AI and HPC chips. Learn about interposers, TSVs, chiplets, and how companies like AMD and NVIDIA leverage this advanced packaging technique.

How Chiplet Packaging Builds an AI Brain

Explore how chiplet packaging creates modular AI processors. Learn about 2.5D/3D stacking, CoWoS, UCIe, ESG strategies, and global foundry trends.

What’s the Difference Between CoWoS-S, CoWoS-R, and CoWoS-L? The Three-Act Evolution of TSMC's Packaging

Learn the differences between TSMC’s CoWoS-S, CoWoS-R, and CoWoS-L packaging technologies, and how they enable the future of AI and HPC.

Why AI Training Chips Can't Live Without CoWoS

Why AI Training Chips Can't Live Without CoWoS: Unpacking the High-Bandwidth Packaging Revolution

AI Is Running Too Fast for Fiber? CPO Is the Lifeline of Data Centers

In the AI era, data transmission is under extreme pressure. How does CPO (Co-Packaged Optics) solve bandwidth bottlenecks and reduce power consumption? Explore Taiwan and global tech strategies.

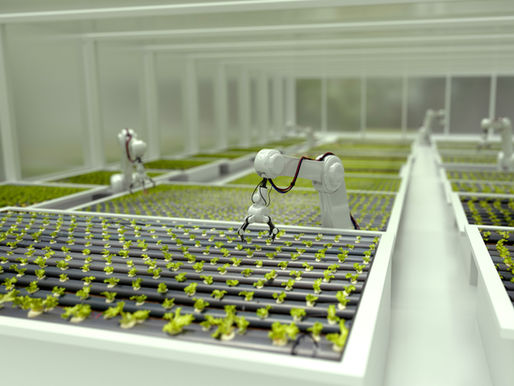

Digital Twin & Robotics: The Cyber-Physical Blueprint of the AI Industrial Revolution

Explore how digital twin technology is reshaping manufacturing, logistics, and aerospace when integrated with robotics—unveiling a future driven by AI, predictive maintenance, and smart factories.

From Gaming to Global Intelligence: How NVIDIA CUDA Built an AI Empire

Explore the architecture and evolution of NVIDIA CUDA—how a graphics chip transformed into a high-performance computing platform driving today’s AI revolution. Discover its design, impact, and future.

Understand CoWoS, HBM, and FOWLP: A Beginner-Friendly Semiconductor Keyword Map

Learn what CoWoS, HBM, FOWLP, GAAFET, Chiplet, RDL, and 2.5D packaging mean. This guide helps you grasp the essential technologies behind AI, chips, and advanced semiconductor integration.

Complete Guide to CoWoS Process: The Key Advanced Packaging Technology for the AI Era

Explore TSMC’s CoWoS (Chip-on-Wafer-on-Substrate) technology in detail, including process steps, interposer design, TSV, RDL, and real-world applications in AI and high-performance computing systems.

CoWoS vs InFO Technology Comparison

Explore the structural differences, applications, and future trends of CoWoS and InFO—TSMC’s leading advanced packaging technologies. This in-depth guide compares thermal performance, power handling, and integration density to help engineers make informed decisions.

Exploring the Future of High-Performance Computing: A Detailed Look at CoWoS Technology

This article will cover the fundamental principles of CoWoS technology, its application areas, market prospects, and the impact of this tech

bottom of page